INTERACT Archive (2014-2019)

JOSEF RESSEL CENTER FOR INTEGRATED CMOS RF SYSTEMS AND CIRCUITS DESIGN

Modern solutions of wireless RF systems require multi-standard multi-band functionality for future software defined radio and agile radio products.

About INTERACT

JOSEF RESSEL CENTER FOR INTEGRATED CMOS RF SYSTEMS AND CIRCUITS DESIGN

Modern solutions of wireless RF systems require multi-standard multi-band functionality for future software defined radio and agile radio products.

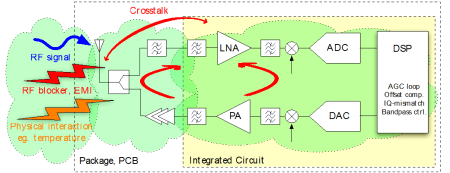

Modern solutions of wireless RF systems require multi-standard multi-band functionality for future software defined radio and agile radio products. The high number of wireless standards implemented in mobile devices (GSM/EDGE, UMTS, LTE, Wi-Fi, GPS, Wireless HD, Wireless USB, NFC, DVB-S2, ….) with preferably single radio architectures creates a number of challenges which are not covered by “classical” RF-circuit design and analog-mixed signal design methodologies only.

A high number of challenges like strong interference between the different RF frontends, a complex interface between the RF integrated circuit, external components and the antenna, as well as limitations of available power, chip area, PCB area and mainly costs needs to be solved for future products.

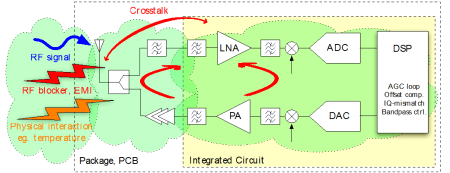

This leads to the necessity of new RF frontend concepts leveraging reconfigurable building blocks using “digitally assisted RF” concepts to cope with non-idealities in the RF performance such as gain control, offset control or noise and crosstalk compensation. These concepts are already quite established in standard low-frequency analog design, while they were hardly used for RF applications in the past. Furthermore, there is strong signal interaction between RF, analog blocks, digital blocks on a system-on-chip (SoC) and external components on package and board level. This requires new multi-disciplinary design and modeling approaches, which are necessary to combine the diverse field of knowledge and tooling used for development of integrated RF systems.

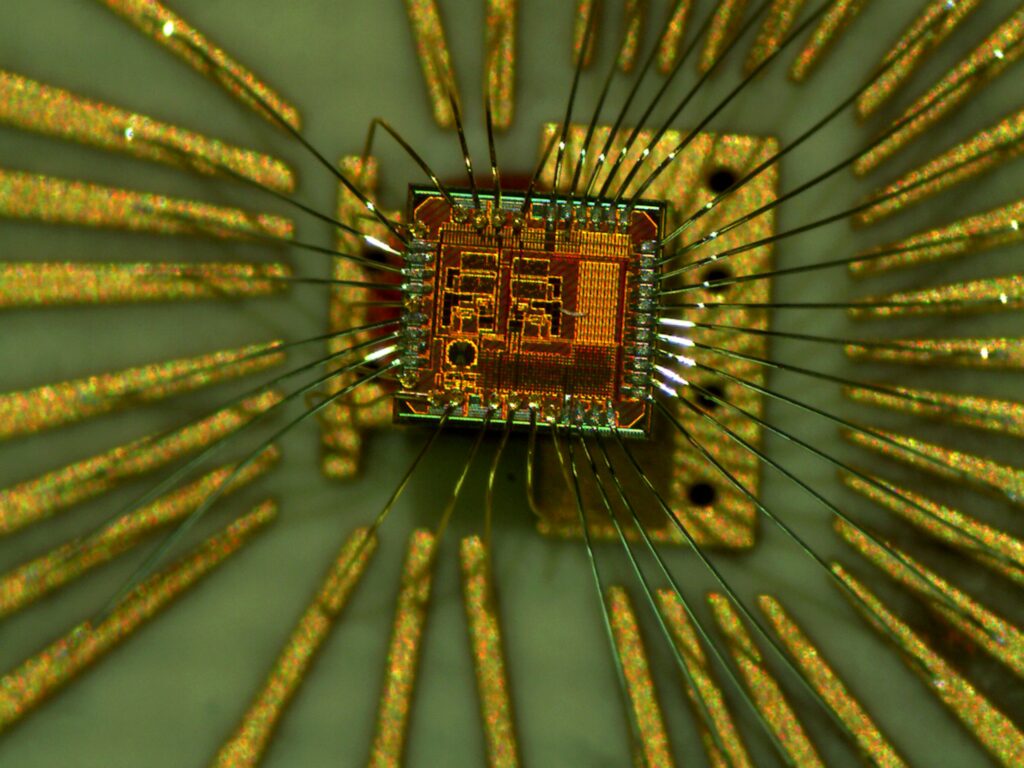

The research activities of the proposed Ressel center at Fachhochschule Kärnten will focus on reconfigurable integrated radio-frequency (RF) systems and circuits based on standard integrated circuit CMOS technologies. Also electromagnetic interference and co-existence issues in modern wireless transceivers will be investigated and improved. The tasks include all necessary development steps like modeling, simulation, circuit implementation and lab characterization, supporting future integrated wireless communication systems.

The focus of proposed Ressel center is illustrated in Figure 1

Goals

INTERACT can offer research expertise and support in the following fields of microelectronics

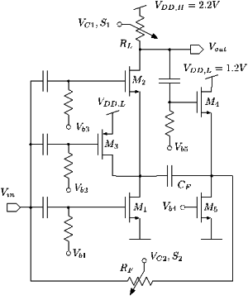

New RF frontend circuit concepts leveraging re-confi gurable building blocks using “digitally assisted RF” will be

researched to cope with non-idealities in the RF performance.

There is strong signal interaction between RF, analog and digital IC blocks as well as to external components in package (System-in-Package SiP) and board level. This requires new multi-disciplinary design and modeling approaches, to combine the diverse fi eld of knowledge and tooling for future integrated RF systems.

Methodology

The research activities at CUAS will focus on re-configurable integrated RF systems and circuits based on standard integrated circuit CMOS technologies. Also electromagnetic interference and co-existence issues in modern wireless transceivers will be investigated and improved. The tasks include all necessary development steps like modeling, simulation, circuit implementation and lab characterization, supporting future integrated wireless communication systems.

Benefits

The Ressel Center INTERACT provides a long term perspective for scientifi c research on a challenging, multidisciplinary topic. It merges diff erent fi elds of knowledge like integrated RF circuit design, modeling of RF systems, digital signal processing and fi nite-element simulations of electromagnetic interactions and crosstalk within modern integrated RF systems.

INTERACT

INTERACT was organized in two Moduls “MODUL 1” and “MODUL 2” focusing on research topics:

MODUL 1

Intel – Connected Home Division

Module 1 is researching RF building blocks together with RF related signal processing and modeling tasks for next generation 802.11ac WLAN transceiver SoC’s. A main focus will be on development of flexible and tunable RF building blocks like LNA’s, mixer, PA’s with interaction to digital signal processing for non-ideality compensation of modern CMOS technologies. The industry partner of Module 1 is Intel – Connected Home Division. The research work of the module is split into three different fields:

- RF Transceiver Design

- RF Signal Processing

- RF Lab Characterization

MODUL 2

Intel – Communication & Devices Group

The focus of module 2 is research on transceiver RF frontend integration aspects like modeling and simulation of electromagnetic interactions between the transceiver IC and external components. Also interference compensation strategies of multi-standard transceivers will be researched. Finally necessary lab evaluation including hardware development will be covered in Module 2. The industry partner of Module 2 is Intel – Communication & Devices Group. The research work of the module is split into three different fields:

- RF System Integration

- Electromagnetic field simulations

- RF and electromagnetic measurements

Output

On-chip re-confi gurable RF components are cheaper than many individual parallel blocks. Also digitally assisted RF blocks are enabling low-cost standard CMOS SoC integration instead of heterogeneous integration of optimized and expensive components. The digital assistance also results in technically superior solutions with smaller silicon area and less power consumption, which results in an overall economical advantage. Finally an accurate modeling of external components including chip interface and electromagnetic interferences will increase the product quality and supports

fi rst-time-right product designs, which leads to signifi cant cost savings.

Outlook

The close cooperation of the Ressel center with important international companies will enable leading edge research in Austria, based on the economically and socially relevant topic of mobile communication.

In addition the Ressel center will have a direct positive impact on

• Know-How increase at school of Engineering & IT at CUAS

• Know-How fl ow to related master courses (ISCD or SD)

• Employment opportunities at CUAS

• Publications at conferences and related scientifi c journals

• Patents portfolio increase

CIME – Carinthia Institute for Microelectronics

The Carinthia Institute for Microelectronics (CIME) is a competence center for research and development of integrated electronic systems. CIME is strongly associated to the department of Integrated Systems and Circuits Design (ISCD) with a srong network to other department within the faculty of Engineering & IT at Carinthia University of Applied Sciences and is also based on the research of Josef Ressel Center “Interact” which was operated at CUAS until 2019.

Publications

- Graciele Batistell, Sina Mortezazadeh Mahani, Suchendranath Popuri, Ajinkya Kale, Johannes Sturm and Wolfgang Bösch, Analysis of Common-mode Isolation on Transformer Based Balun, Proc. 27th Austrochip Conference, pp. 71-74, Vienna, 2019. DOI: 10.1109/Austrochip.2019.00024

- Ram Ratnaker Reddy Bodha, Sahar Sarafi, Ajinkya Kale, Michael Köberle and Johannes Sturm, A Half-Rate Built-In Self-Test for High-Speed Serial Interface using a PRBS Generator and Checker, Proc. 27th Austrochip Conference, pp. 43-46, Vienna, 2019 DOI: 10.1109/Austrochip.2019.00019

- Arash Ebrahimi Jarihani, Sahar Sarafi, Michael Köberle, Johannes Sturm and Andrea M. Tonello, Characterization of On-Chip Interconnects: Case Study in 28 nm CMOS Technology, Proc. 27th Austrochip Conference, pp. 93-98, Vienna, 2019. DOI: 10.1109/Austrochip.2019.00028

- Plattner, S. L. Lattacher, D. Krainer, J. Oberzaucher, G. Batistell, J. Sturm, Entwicklung drahtloser Sensorsysteme durch synergetische Nutzung interdisziplinärer sowie grundlagenorientierter Forschungskonzepte, e&i Elektrotech. Inftech., Springer Wien, (2019). https://doi.org/10.1007/s00502-019-00777-6

- Ajinkya Kale, Graciele Batistell, Suchendranath Popuri, Vijaya Sankara Rao Pasupureddi, Wolfgang Boesch, Johannes Sturm, Integration Solutions for Reconfigurable Multi-Standard Wireless Transceivers, , e&i elektrotechnik und Informationstechnik, Springer Wien, 2018. DOI: https://doi.org/10.1007/s00502-018-0595-6

- Ajinkya Kale, Johannes Sturm and Vijaya Sankara Rao Pasupureddi, 0.9 to 2.5 GHz Sub-sampling Receiver Architecture for Dynamically Reconfigurable SDR, IEEE Computer Society Annual Symposium on VLSI (ISVLSI 2018), Hong Kong, 2018. DOI: 10.1109/ISVLSI.2018.00065

- Abdelhamed Eldeeb, Graciele Batistell and Johannes Sturm, SCPA Transformer Based Matching Network Design Flow and SiP Implementation, Proc. 26th Austrochip Conference, Graz, 2018. DOI: 10.1109/Austrochip.2018.8520704

- Ivan Sejc, Suchendranath Popuri and Johannes Sturm, Design of DAC Based RMS Power Detector for RF Application, Proc. 26th Austrochip Conference, Graz, 2018. DOI: 10.1109/Austrochip.2018.8520707

- Graciele Batistell, Ajinkya Kale and Johannes Sturm, SCPA non-linearity Modelling and Analysis, International Workshop on Integrated Nonlinear Microwave and Millimetre-wave Circuits (INMMiC 2018), France, 2018. DOI: 10.1109/INMMIC.2018.8429993

- Ajinkya Kale, Vijaya Sankara Rao Pasupureddi, Johannes Sturm, −40 dB EVM 20 MHz Subsampling Multi-Standard Receiver Architecture with Dynamic Carrier Detection, Bandwidth Estimation and EVM Optimization, International Journal of Circuit Theory and Applications, Wiley 2019. https://doi.org/10.1002/cta.2601

- Ajinkya Kale, Suchendranath Popuri, Michael Koeberle, Johannes Sturm and Vijaya Sankara Rao Pasupureddi, A −40 dB EVM, 77 MHz Dual-Band Tunable Gain Sub-Sampling Receiver Front End in 65-nm CMOS, IEEE Transactions on Circuits and Systems-I, 2018. DOI: 10.1109/TCSI.2018.2878342

- G. Batistell, T. Holzmann, S. Leuschner, A. Wolter, A Passamani, J.Sturm, SiP Solutions for Wireless Transceiver Impedance Matching Networks, Proc. European Microwave Conference, pp. 1069-1072, 2017

- A. Kale, S.Popuri, M.Koeberle, J. Sturm and V. S. R. Pasupureddi, Sub-sampling Receiver for IEEE 802.11ac, 5th Work-shop of the Radio Frequency Engineering Working Group of the Austrian Research Association, Vienna, Sept 2017.

- G. Batistell, J. Sturm and W. Boesch, CMOS Integrated Duplexer based on SIC for IoT Transceiver, in 5th Work-shop of the Radio Frequency Engineering Working Group of the Austrian Research Association, Vienna, Sept 2017.

- Popuri, V. S. R. Pasupureddi and J. Sturm, A Tunable Gain and Tunable Band Active Balun

- LNA for IEEE 802.11ac WLAN Receivers, Proc. 42nd European Solid-State Circuits Conference, Lausanne, pp.185-188, 2016. DOI: 10.1109/ESSCIRC.2016.7598273

- Timo Holzmann, Graciele Batistell, Hermann Sterner and Johannes Sturm, Algorithms for De-embedding of RF Measurement Data for Balanced and Unbalanced Setups, Proc. 52nd Conference on Microelectronics, Devices and Materials (MIDEM), Slovenia, 2016

- Batistell, T. Holzmann, H. Sterner and J. Sturm, System-in-Package Matching Network for RF Wireless Transceivers, Proc. 24th Austrochip Conference, pp. 35-39,2016. DOI: 10.1109/Austrochip.2016.018

- T. Renukaswamy, V. Pasupureddi and J. Sturm, Analysis and Design of Differential Feedback CG LNA Topologies for Low Voltage Multistandard Wireless Receivers, Proc. 24th Austrochip Conference, pp. 24-29, 2016. DOI: 10.1109/Austrochip.2016.016

- Shetty, V. Pasupureddi and J. Sturm, A 2.4 GHz, 1 dB Noise Figure Common-Gate LNA for WLAN Frontend, Proc. 24th Telecommunications Forum TELFOR 2016, 2016. DOI: 10.1109/TELFOR.2016.7818863

- Kale, V. Sankara, R. Pasupureddi, and J. Sturm, Dynamically Reconfigurable Multiband Subsampling Receiver Architecture, 4th Workshop Radio Frequency Engineering Working Group of Austrian Research Association, Oct. 2016

- Popuri, V. Pasupureddi, and J. Sturm, A Tunable Gain and Tunable Band Active Balun LNA for IEEE 802.11ac WLAN Receivers, 4th Workshop Radio Frequency Engineering Working Group of Austrian Research Association, Oct. 2016

- Batistell and J. Sturm, System-in-Package Matching Network for RF Wireless Transceivers, 4th Workshop Radio Frequency Engineering Working Group of Austrian Research Association, Oct. 2016

- Drago Strle, Uroš Nahtigal, Graciele Batistell, Vincent Chi Zhang, Erwin Ofner, Andrea Fant, Johannes Sturm, Integrated High Resolution Digital Color Light Sensor in 130 nm CMOS Technology, MDPI Sensors, Vol. 15, Issue 7, pp. 17786-17807, July 2015. DOI: 10.3390/s150717786

- Sturm, S. Popuri, X. Xiang, A 65 nm CMOS resistive feedback noise canceling LNA with tunable bandpass from 4.6 to 5.8 GHz, Analog Integr. Circuits Signal Process., Springer, 2015. DOI: https://doi.org/10.1007/s10470-015-0658-0

- Aichholzer, J.Sturm, A 65nm CMOS RF Power Detector with Integrated Offset Storage, Proc. Austrochip Conference, 2009.

- Dali, J. Sturm, Design Of A Reconfigurable Gain Lownoise Amplifier For Multistandard Receivers In 65nm Technology, e&i elektrotechnik und Informationstechnik, Springer Wien pp.78-85, 2010. DOI 10.1007/s00502-010-0725-2

- Dali, X. Wang, W. Aichholzer, J. Sturm, Wideband LNAs with Noise and Distortion Cancelation, Proc. Austrochip Conference, pp. 27-31, 2010.

- Xinbo, J. Sturm, CMOS Active Resistor for RF Applications, Proc. Austrochip Conference, pp. 37-41, 2010.

- Batistell, J. Sturm, Lateral Junction Color Detector in Standard CMOS Technology, Proc. Austrochip Conference, pp. 109-113, 2010.

- Wang, W. Aichholzer, J. Sturm, A 0.1-4GHz Resistive Feedback LNA with Feedforward Noise and Distortion Cancelation”, Proc. 36th European Solid-State Circuits Conference, pp. 406-409, 2010. DOI: 10.1109/ESSCIRC.2010.5619729

- Shravan Kumar Kada, David Astrom, Johannes Sturm, Temperature and Process Compensated Oscillator in 0.13μm CMOS IC Technology, Proc. Austrochip Conference, pp. 21-25, 2011.

- Matvey Geldin, Andrea Fant, Johannes Sturm, Second Order Effects in Multislope A/D Converters, Proc. Austrochip Conference, pp. 11-15, 2011.

- Sturm, Reconfigurable CMOS RF-Frontends, IEEE Froum on Signal Processing for Radio Frequency Systems, 2011.

- Xiang, J. Sturm, Tunable Linear MOS Resistor for RF Applications, Silicon Monolithic Integrated Circuits in RF Systems, 2012. DOI: 10.1109/SiRF.2012.6160119

- Xiang, J. Sturm, Performance Study of a 65nm CMOS Tuneable Gain LNA, Proc. Austrochip Conference, pp. 47-50, 2012.

- Xiao Wang, Johannes Sturm, Na Yan, Xi Tan, and Hao Min, 0.6–3-GHz Wideband Receiver RF Front-End With a Feedforward Noise and Distortion Cancellation Resistive-Feedback LNA, IEEE Trans. Microw. Theory Techn., Vol. 60, No. 2 , pp. 387-392, 2012. DOI: 10.1109/TMTT.2011.2176138

- Sturm, X. Xinbo, H. Pretl, A 65nm CMOS Wide-band LNA with ContinuouslyTunable Gain from 0dB to 24dB, IEEE International Symposium on Circuits and Systems – ISCAS, pp. 733-736, 2013. DOI: 10.1109/ISCAS.2013.6571951

- Batistell, J. Sturm, Filter-less Color Sensor in Standard CMOS Technology, Proc. 43th European Solid-State Device Research Conference – ESSDERC, pp. 123-126, 2013. DOI: 10.1109/ESSDERC.2013.6818834

- Batistell, J. Sturm, Simulation and Implementation of a Filter-less CMOS Color Detector, Proc. 49th Conference on Microelectronics, Devices and Materials (MIDEM), pp. 167-172, 2013

- Batistell, J. Sturm, Standard CMOS Color Sensor based on laterally and vertically arranged photodiodes, Proc. Austrochip Conference, pp. ????, 2013.

- Sturm, M. Groinig, X. Xiang, Tunable Balun Low-Noise Amplifier in 65nm CMOS Technology, Radioengineering, Vol. 23, No. 1, pp. 319-327, April 2014. Corpus ID: 625807

- Batistell, V.C. Zhang, J. Sturm, Color recognition sensor in standard CMOS technology. Solid State Electronics, Vol. 102, pp. 59-68, 2014. DOI: 10.1016/j.sse.2014.06.002

- Sturm, G. Batistell, L.M. Faller, V.C. Zhang, Integrated CMOS Optical Sensor for Light Spectral Analysis, IEEE J. Sel. Topics Quantum Electron., Vol. 20, Issue: 6, Nov. 2014. DOI: 10.1109/JSTQE.2014.2344032

- Sturm, G. Batistell, Highly Integrated Low-Cost Color Sensors, Proc. 8. Forschungsforum der österreichischen Fachhochschulen, April 2014, ISBN: 978-3-9503491-9-1

- Batistell, J. Sturm, A. Fant, D. Strle, Color Sensor for Ambient Light Measurements in 130nm CMOS Technology, Proc. 50th Conference on Microelectronics, Devices and Materials (MIDEM), 2014

- C. Zhang, E. Ofner, Dušan Raič, J. Sturm, A. Fant, D. Strle, Decimation Filter and Tri-stimulus Colour Transformation for Ambient Colour Light Sensor, Proc. 50th Conference on Microelectronics, Devices and Materials (MIDEM), 2014

- Popuri, J. Sturm, A Wideband Resistive Feedback Balun LNA in 65 nm CMOS Technology, Proc. 22nd Austrochip Conference, pp. 59-62, 2014. DOI: 10.1109/Austrochip.2014.6946322

- Sturm, Monolithic Integrated Color Sensor in CMOS Nano Technologies, Proc. Int. Conference on functional Integrated Nanosystems – nanoFIS, Graz, 2014

- Sturm, S. Popuri, X. Xiang, CMOS Noise Canceling Balun LNA with Tunable Bandpass from 4.6 GHz to 5.8 GHz, Proc. 21st IEEE International Conference on Electronics Circuits and Systems, Marseille, 2014. DOI: 10.1109/ICECS.2014.7049927

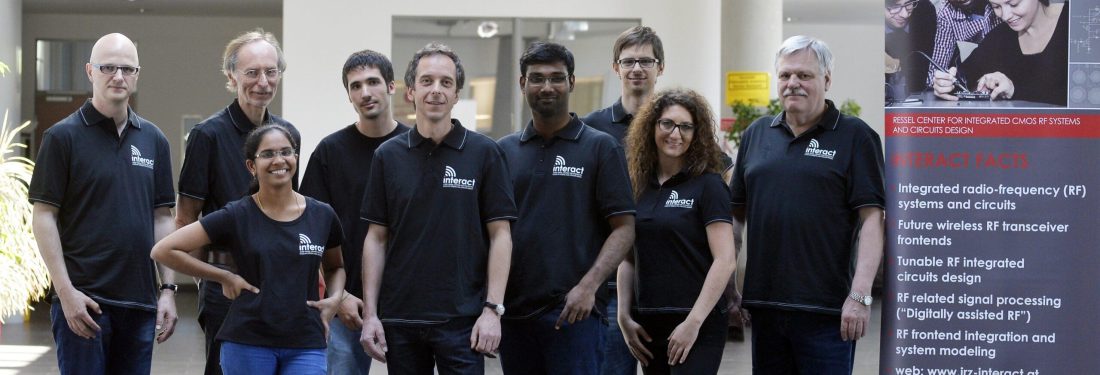

Team

FH-Prof. DI Dr.

Johannes Sturm

Lead: CIME & RFFE Labs (Head of JR Center INTERACT)

Carinthia University of Applied Science,

Europastrasse 4, 9500 Villach

j.sturm@fh-kaernten.at

Employee profile

Graciele Batistell, Ph.D.

Researcher, Module leader

Carinthia University of Applied Science,

Europastrasse 4, 9500 Villach

Suchendranath Popuri, MSC

Researcher, Module leader

Carinthia University of Applied Science,

Europastrasse 4, 9500 Villach

s.popuri@fh-kaernten.at

Employee profile

Mag. Angelika Voutsinas

Assistant, Financial Support / FH Kärnten Research Center

Carinthia University of Applied Science,

Europastrasse 4, 9500 Villach

a.voutsinas@fh-kaernten.at

Employee profile

Partner/Cooperation

Initially our Ressel Center started with project partner Lantiq A GmbH at 01.04.2014.

Lantiq A GmbH and Intel Mobile Communications Austria GmbH were merged in November 2015 to Intel Austria GmbH. Therefore our project partner is now the “Connected Home Devision” of Intel. Lantiq has a 20+ year record of technology leadership, innovation, and strong customer relationships. Its holistic understanding of broadband technology, complete applications, communication standards, and legacy networks enables the company to offer the broadest portfolio of highly integrated, flexible end-to-end semiconductor solutions for next generation networks and the digital home. Backed by excellent support, Lantiq’s solutions enable global system manufacturers to gain a commercial edge and create high-speed data and communication products which drive innovation in this market and deliver value to carriers and operators. Lantiq’s solutions are deployed by major carriers and found in access networks and home networks in every region of the world. Lantiq’s advanced SoC (system-on-chip) solutions address a wide variety of technologies, including all flavors of xDSL, VoIP, wireless LAN and Gigabit Ethernet, and have allowed Lantiq to become the number one supplier of access network integrated circuits. As a private company, its investor is Golden Gate Capital, a leading private equity firm. Also T-Venture, the venture capital firm of Deutsche Telekom, made a strategic investment in Lantiq. The company is an international fabless semiconductor organization of approximately 800 people. Approximately 70% of Lantiq’s staff consists of R&D engineers. A significant part of Lantiq’s R&D and most of the central functions and executive management are located in Neubiberg (Munich), Germany. The Main R&D locations are in: Europe – Munich, Villach, Riga, Yakum, Asia Pacific – Hsinchu, Singapore and Bangalore.

Intel Austria GmbH. – Communication & Devices Group

Intel Mobile Communications as our “second” partner is now part of Intel’s Communication & Devices Group. It develops, manufactures and markets end-to-end, leading-edge semiconductor products and solutions for wireless communications. IMC’s goal is to enable the smooth transmission of voice and high-speed data to the end-user’s equipment. IMC offers a mature portfolio of RF transceivers, cellular platforms, and connectivity solutions for mobile phones, smartphones, and mobile computing devices. Leveraging its unique advantages in the areas of RF and mixed-signal expertise, monolithic integration capabilities, and excellent knowhow in cellular software and systems, IMC provides superior customer solutions. Intel Mobile Communications Austria GmbH is located in Villach in the south of Austria. Founded in 2011, nearly 40 employees work on CMOS Circuit Development and IT R&D Application and System Architecture. As a part of the Intel Mobile Communications Group, we contribute with our strong RF and Mixed Signal Expertise to signal processing solutions for LTE, UMTS, GSM, WIFI, BT standards. We provide the complete set of expertise including System Engineering, Circuit Design, Physical Design and Component Verification for MCGs wireless product portfolio. A well-developed and innovative lab area ensures the verification of ADCs and DACs for cellular applications.